UALink 200G v1.0 Verification IP

Truechip's UALink 1.0 Verification IP provides an effective & efficient way to verify the components interfacing with the UALink interface of an ASIC/FPGA or SoC. Truechip's UALink VIP is fully compliant with the Standard UALink Version 1.0 specification from the UALink consortium. This VIP is a lightweight VIP with an easy plug-and-play interface, so that there is no hit on the design time and the simulation time.

Key Benefits

- Available in native System Verilog (UVM/OVM/ VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity example for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Features

- Fully compliant with the UALink V1.0 specification from the UALink consortium

- Supports the UPLI interface operating in both Originator and Completer device modes.

- Supports all defined request types, including Read, Write, AtomicR, and AtomicNR operations.

- Supports a fully credit-based flow control mechanism for all request types.

- Supports Transaction Layer (TL) Tx and Rx address cache synchronization.

- Supports compressed and uncompressed request and response formats at the Transaction Layer (TL).

- Supports FLIT-to-64B/66B encoding functionality.

- Supports Tx pacing, Rx rate adaptation, DL message service, FLIT packing, and link-level replay features.

- The PHY Layer (PL) is compliant with IEEE 802.3dj Ethernet PHY specifications.

- Supports link widths: x1, x2, and x4.

- Supports all link speeds:

- 100G, 200G, and 400G with 100G per lane

- 200G, 400G, and 800G with 200G per lane.

- Supports 1-way, 2-way, and 4-way codeword interleave modes.

- Supports lane bifurcation, enabling a port to be divided into multiple independent UALinks.

- Supports on-the-fly link speed and link width changes within a single test.

- Supports AES-GCM encryption and authentication.

- Supports RS-FEC RS(544,514) codeword encoding and decoding as per the Ethernet PHY specification.

- Supports Auto-Negotiation and Link Training (AN/LT) as defined in IEEE 802.3, without modification.

- Callback support in BFM to provide user control

- Supports Dynamic as well as Static Error Injection scenarios Strong Protocol Monitor with real time exhaustive, programmable checks

- Supports dynamically configurable modes

- On-the-fly protocol checking using protocol check functions, static and dynamic assertions

- Built in Coverage analysis.

- Graphical analyzer to show transactions for easy debugging

Deliverables

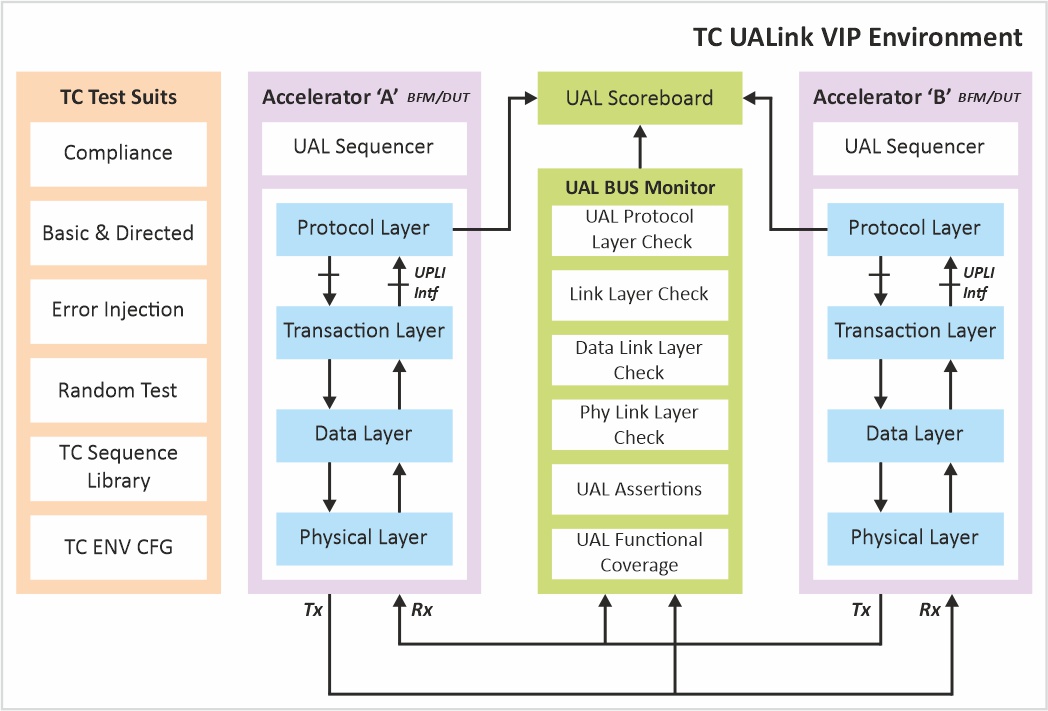

- UALink BFM's/Agents

- Protocol Layer

- Transaction Layer

- Data Link Layer

- Physical Layer

- UALink Switch devices

- UALink Layered Monitors and Scoreboard

- Integration Guide, User Manual and Release Notes

- GUI analyser to view simulation packet flow

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Coverage Tests

- User Test Suite